## M.Tech. Degree Examination, December 2011 Synthesis and Optimization of Digital Circuits

Time: 3 hrs.

Max. Marks:100

## Note: Answer any FIVE full questions.

- a. Draw the Y chart for different level of abstraction and synthesis. Explain different levels

- b. Implement 2 = a b c d using two input AND or three input AND gates. Assume gate area and delays are proportional to the number of inputs. Draw the circuit and design space graph for 4 types of implementation. (06 Marks)

- What are the various tasks performed in physical design? Explain briefly.

(04 Marks)

- a. Define the following with respect to concept of graph theory and write an example for each. ii) Hyper graph. i) Directed graph

- b. What is meant by stability number and chromic number of a graph? Show that the graph shown in fig.Q2(b) is a perfect graph. (06 Marks)

- c. Write Pseudo code for greedy scheduling algorithm and explain with an example. (10 Marks)

- Write BDD for f = (a + b)c and obtain ROBDD for the same.

(06 Marks)

b. Write silage code for recursive filter.

(06 Marks)

Write data flow graph and sequencing graph for the model shown:

$$a_1 = (3*x + 4*y)*(8*z)$$

;

$b_1 = (8*y) + 3$ ;

$$c_1 = b1 \ge c$$

;  $d_1 = 2 * x - 8$ .

(08 Marks)

- a. Find minimum cover for the following function using exact logic minimization algorithm. (08 Marks)

- $f = \sum m_0$ ,  $m_2$ ,  $m_4$ ,  $m_6$ ,  $m_8$ ,  $m_{10}$ ,  $m_5$ ,  $m_7$ ,  $m_9$ ,  $m_{11}$ ,  $m_{13}$ . b. Determine  $F^{ON}$ ,  $F^{DC}$  and  $F^{OFF}$  set in positional cube notation for the function f = a'b'c' + ab'c' + a'be' + a'b'c with abc' as 0 don't care condition. Fund minimum cover using expand and reduce operator. (12 Marks)

- a. Write Pseudo code for ASAP and ALAP used for scheduling.

- b. Obtain scheduled graph for the following model using list scheduling algorithm. Assume (10 Marks) there are 3 multipliers and 1 ALU and unit execution delay.

$$a1 = x + dx$$

;  $a2 = u - (3 * x * u * dx) - (3 * y * dx)$ ;

$a3 = y + u*dx$   $a4 = a1 < b$ .

(10 Marks)

a. A logic network has 5 primary inputs (a, b, c, d, c) and 4 primary outputs (w, x, y, z). The logic network is defined by

$$p = cc + dc$$

;  $q = a + b$ ;  $r = p + a'$ ;  $s = r + b'$ ;

$$t = ac + ad + bc + bd + e$$

;  $u = q'c + qc' + qc$ ;

- w = v; x = s; y = t; z = u; Obtain logic transformation elimination, decomposition and extraction. (12 Marks)

- b. Compute Kernels and Co-Kernels based on matrix representation for f = ace + bce + de + g.

(08 Marks)

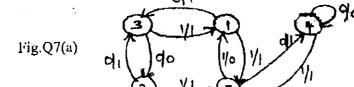

- 7 a. For the state diagram, shown in fig.Q7(a), find minimum state diagram.

(10 Marks)

b. Explain anyone ATPG method with neat diagram.

(10 Marks)

- 8 Write short notes on:

- a. Dijkstra algorithm.

- b. II.P model for scheduling.

- c. Tree based matching.

- d. Rule based library binding.

(20 Marks)

\*\*\*\*